# $^{\prime}$ 24-Bit High Speed Differential $\Delta\Sigma$ ADC with Selectable Speed/Resolution

#### **FEATURES**

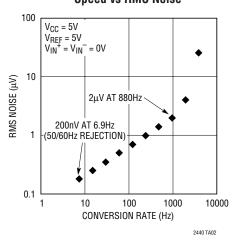

- Up to 3.5kHz Output Rate

- Selectable Speed/Resolution

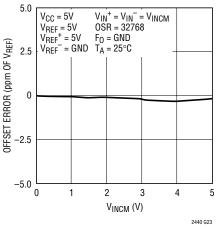

- 2μV<sub>RMS</sub> Noise at 880Hz Output Rate

- 200nV<sub>RMS</sub> Noise at 6.9Hz Output Rate with Simultaneous 50/60Hz Rejection

- 0.0005% INL, No Missing Codes

- Autosleep Enables 20µA Operation at 6.9Hz

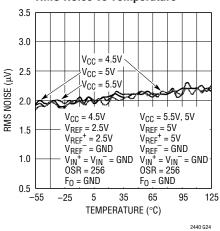

- $<5\mu V$  Offset  $(4.5V < V_{CC} < 5.5V, -40^{\circ}C$  to  $85^{\circ}C)$

- Differential Input and Differential Reference with GND to V<sub>CC</sub> Common Mode Range

- No Latency, Each Conversion is Accurate Even After an Input Step

- Internal Oscillator—No External Components

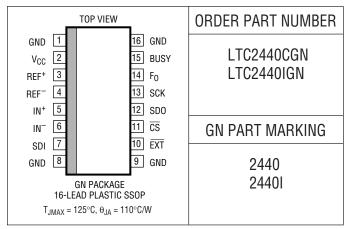

- 24-Bit ADC in Narrow 16-Lead SSOP Package

- Pin Compatible with the LTC2410

#### **APPLICATIONS**

- High Speed Multiplexing

- Weight Scales

- Auto Ranging 6-Digit DVMs

- Direct Temperature Measurement

- High Speed Data Acquisition

#### DESCRIPTION

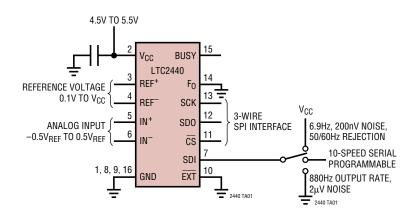

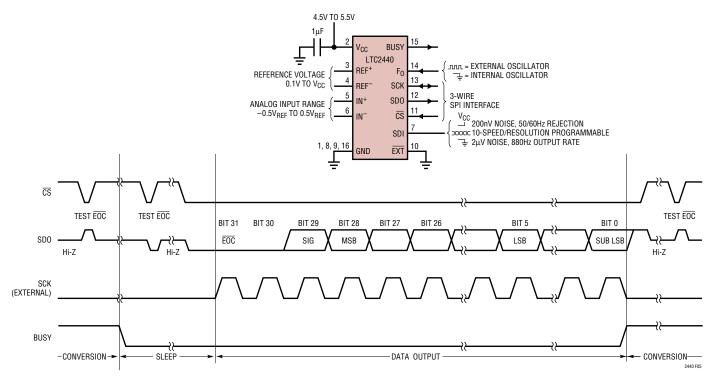

The LTC®2440 is a high speed 24-bit No Latency  $\Delta\Sigma^{\text{TM}}$  ADC with 5ppm INL and 5 $\mu$ V offset. It uses proprietary deltasigma architecture enabling variable speed and resolution with no latency. Ten speed/resolution combinations (6.9Hz/200nV<sub>RMS</sub> to 3.5kHz/25 $\mu$ V<sub>RMS</sub>) are programmed through a simple serial interface. Alternatively, by tying a single pin HIGH or LOW, a fast (880Hz/2 $\mu$ V<sub>RMS</sub>) or ultralow noise (6.9Hz, 200nV<sub>RMS</sub>, 50/60Hz rejection) speed/resolution combination can be easily selected. The accuracy (offset, full-scale, linearity, drift) and power dissipation are independent of the speed selected. Since there is no latency, a speed/resolution change may be made between conversions with no degradation in performance.

Following each conversion cycle, the LTC2440 automatically enters a low power sleep state. Power dissipation may be reduced by increasing the duration of this sleep state. For example, running at the 3.5kHz conversion speed but reading data at a 100Hz rate draws  $240\mu$ A average current (1.1mW) while reading data at 7Hz output rate draws only  $25\mu$ A (125 $\mu$ W).

The LTC2440 communicates through a flexible 3- or 4-wire digital interface that is compatible with the LTC2410.

$\Delta T$ , LTC and LT are registered trademarks of Linear Technology Corporation. No Latency  $\Delta \Sigma$  is a trademark of Linear Technology Corporation.

# TYPICAL APPLICATION

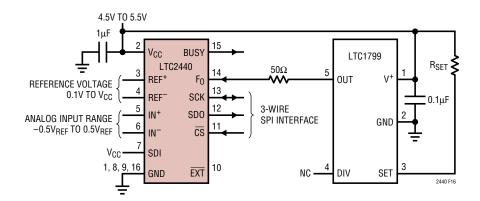

#### Simple 24-Bit 2-Speed Acquisition System

#### **Speed vs RMS Noise**

2440i

# **ABSOLUTE MAXIMUM RATINGS**

| (Notes 1, 2)                                               |

|------------------------------------------------------------|

| Supply Voltage (V <sub>CC</sub> ) to GND0.3V to 7V         |

| Analog Input Pins Voltage                                  |

| to GND $-0.3V$ to $(V_{CC} + 0.3V)$                        |

| Reference Input Pins Voltage                               |

| to GND $-0.3V$ to $(V_{CC} + 0.3V)$                        |

| Digital Input Voltage to GND $-0.3V$ to $(V_{CC} + 0.3V)$  |

| Digital Output Voltage to GND $-0.3V$ to $(V_{CC} + 0.3V)$ |

| Operating Temperature Range                                |

| LTC2440C0°C to 70°C                                        |

| LTC2440I40°C to 85°C                                       |

| Storage Temperature Range65°C to 150°C                     |

| Lead Temperature (Soldering, 10 sec)300°C                  |

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Notes 3, 4)

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                                                                        |   | MIN | TYP            | MAX      | UNITS                                                                         |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----------------|----------|-------------------------------------------------------------------------------|

| Resolution (No Missing Codes)   | $0.1V \le V_{REF} \le V_{CC}$ , $-0.5 \cdot V_{REF} \le V_{IN} \le 0.5 \cdot V_{REF}$ , (Note 5)                                                                                                                                                                  | • | 24  |                |          | Bits                                                                          |

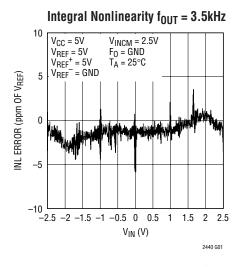

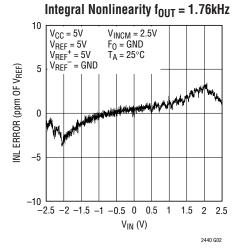

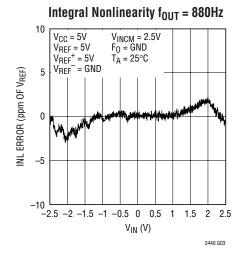

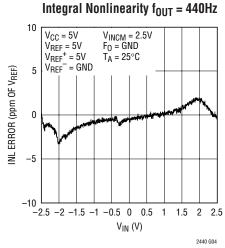

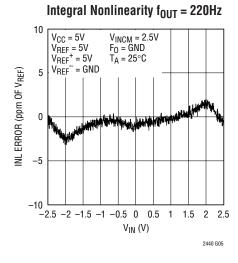

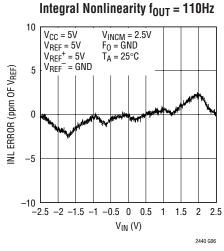

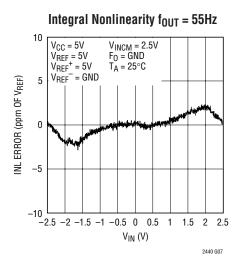

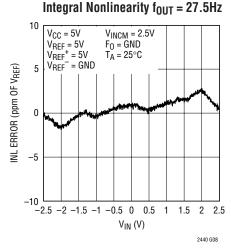

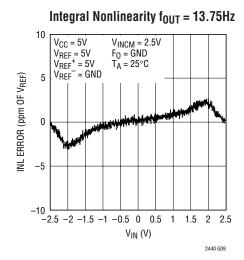

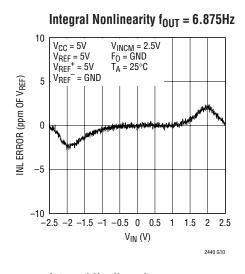

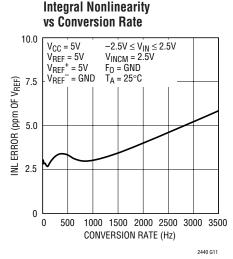

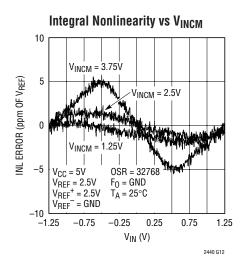

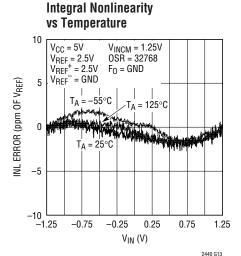

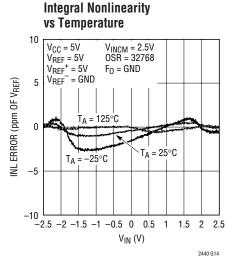

| Integral Nonlinearity           | $V_{CC} = 5V$ , REF <sup>+</sup> = 5V, REF <sup>-</sup> = GND, $V_{INCM} = 2.5V$ , (Note 6)<br>REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, $V_{INCM} = 1.25V$ , (Note 6)                                                                                     | • |     | 5<br>3         | 15       | ppm of V <sub>REF</sub>                                                       |

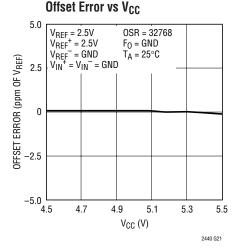

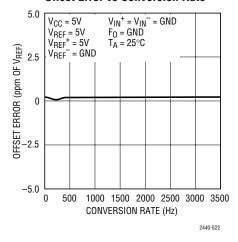

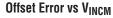

| Offset Error                    | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>$GND \le IN^+ = IN^- \le V_{CC}$ (Note 12)                                                                                                                                                                       | • |     | 2.5            | 5        | μV                                                                            |

| Offset Error Drift              | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>$GND \le IN^+ = IN^- \le V_{CC}$                                                                                                                                                                                 |   |     | 20             |          | nV/°C                                                                         |

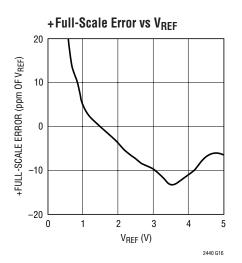

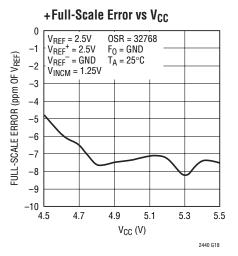

| Positive Full-Scale Error       | REF <sup>+</sup> = 5V, REF <sup>-</sup> = GND, IN <sup>+</sup> = 3.75V, IN <sup>-</sup> = 1.25V<br>REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, IN <sup>+</sup> = 1.875V, IN <sup>-</sup> = 0.625V                                                            | • |     | 10<br>10       | 30<br>50 | ppm of V <sub>REF</sub>                                                       |

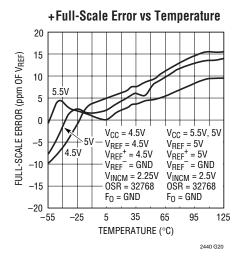

| Positive Full-Scale Error Drift | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>$IN^+ = 0.75REF^+$ , $IN^- = 0.25 \bullet REF^+$                                                                                                                                                                 |   |     | 0.2            |          | ppm of V <sub>REF</sub> /°C                                                   |

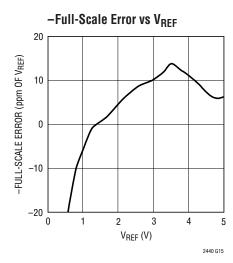

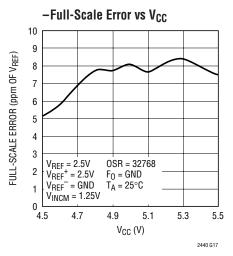

| Negative Full-Scale Error       | REF <sup>+</sup> = 5V, REF <sup>-</sup> = GND, IN <sup>+</sup> = 1.25V, IN <sup>-</sup> = 3.75V<br>REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, IN <sup>+</sup> = 0.625V, IN <sup>-</sup> = 1.875V                                                            | • |     | 10<br>10       | 30<br>50 | ppm of V <sub>REF</sub>                                                       |

| Negative Full-Scale Error Drift | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ , $IN^+ = 0.25 \bullet REF^+$ , $IN^- = 0.75 \bullet REF^+$                                                                                                                                                           |   |     | 0.2            |          | ppm of V <sub>REF</sub> /°C                                                   |

| Total Unadjusted Error          | $\begin{array}{l} 5V \leq V_{CC} \leq 5.5V, \ REF^{+} = 2.5V, \ REF^{-} = GND, \ V_{INCM} = 1.25V \\ 5V \leq V_{CC} \leq 5.5V, \ REF^{+} = 5V, \ REF^{-} = GND, \ V_{INCM} = 2.5V \\ REF^{+} = 2.5V, \ REF^{-} = GND, \ V_{INCM} = 1.25V, \ (Note 6) \end{array}$ |   |     | 15<br>15<br>15 |          | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub> |

| Input Common Mode Rejection DC  | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>$GND \le IN^- = IN^+ \le V_{CC}$                                                                                                                                                                                 |   |     | 120            |          | dB                                                                            |

# **ANALOG INPUT AND REFERENCE** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL                                   | PARAMETER                                          | CONDITIONS                                                        |   | MIN                  | TYP | MAX                    | UNITS |

|------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|---|----------------------|-----|------------------------|-------|

| IN+                                      | Absolute/Common Mode IN+ Voltage                   |                                                                   | • | GND - 0.3V           |     | V <sub>CC</sub> + 0.3V | V     |

| IN <sup>-</sup>                          | Absolute/Common Mode IN <sup>-</sup> Voltage       |                                                                   | • | GND - 0.3V           |     | V <sub>CC</sub> + 0.3V | V     |

| $V_{IN}$                                 | Input Differential Voltage Range (IN+ – IN-)       |                                                                   | • | -V <sub>REF</sub> /2 |     | V <sub>REF</sub> /2    | V     |

| REF+                                     | Absolute/Common Mode REF+ Voltage                  |                                                                   | • | 0.1                  |     | $V_{CC}$               | V     |

| REF-                                     | Absolute/Common Mode REF <sup>-</sup> Voltage      |                                                                   | • | GND                  |     | $V_{\rm CC}-0.1V$      | V     |

| V <sub>REF</sub>                         | Reference Differential Voltage Range (REF+ – REF-) |                                                                   | • | 0.1                  |     | V <sub>CC</sub>        | V     |

| C <sub>S</sub> (IN <sup>+</sup> )        | IN+ Sampling Capacitance                           |                                                                   |   |                      | 5   |                        | pF    |

| C <sub>S</sub> (IN <sup>-</sup> )        | IN <sup>-</sup> Sampling Capacitance               |                                                                   |   |                      | 5   |                        | pF    |

| C <sub>S</sub> (REF <sup>+</sup> )       | REF <sup>+</sup> Sampling Capacitance              |                                                                   |   |                      | 5   |                        | pF    |

| C <sub>S</sub> (REF <sup>-</sup> )       | REF <sup>-</sup> Sampling Capacitance              |                                                                   |   |                      | 5   |                        | pF    |

| I <sub>DC_LEAK</sub> (IN+)               | IN+ DC Leakage Current                             | $\overline{CS} = V_{CC}, IN^+ = GND$                              | • | -100                 | 10  | 100                    | nA    |

| I <sub>DC_LEAK</sub> (IN <sup>-</sup> )  | IN <sup>-</sup> DC Leakage Current                 | $\overline{\text{CS}} = V_{\text{CC}}, \text{ IN}^- = \text{GND}$ | • | -100                 | 10  | 100                    | nA    |

| I <sub>DC_LEAK</sub> (REF+)              | REF+ DC Leakage Current                            | $\overline{\text{CS}} = V_{\text{CC}}, \text{ REF}^+ = 5V$        | • | -100                 | 10  | 100                    | nA    |

| I <sub>DC_LEAK</sub> (REF <sup>-</sup> ) | REF <sup>-</sup> DC Leakage Current                | $\overline{\text{CS}} = V_{\text{CC}}, \text{REF}^- = \text{GND}$ | • | -100                 | 10  | 100                    | nA    |

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL          | PARAMETER                                    | CONDITIONS                                  |   | MIN                    | TYP | MAX  | UNITS |

|-----------------|----------------------------------------------|---------------------------------------------|---|------------------------|-----|------|-------|

| V <sub>IH</sub> | High Level Input Voltage CS, F <sub>0</sub>  | $4.5V \le V_{CC} \le 5.5V$                  | • | 2.5                    |     |      | V     |

| V <sub>IL</sub> | Low Level Input Voltage CS, F <sub>0</sub>   | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V               | • |                        |     | 0.8  | V     |

| V <sub>IH</sub> | High Level Input Voltage<br>SCK              | $4.5V \le V_{CC} \le 5.5V \text{ (Note 8)}$ | • | 2.5                    |     |      | V     |

| V <sub>IL</sub> | Low Level Input Voltage<br>SCK               | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V (Note 8)      | • |                        |     | 0.8  | V     |

| I <sub>IN</sub> | Digital Input Current CS, F <sub>0</sub>     | $0V \le V_{IN} \le V_{CC}$                  | • | -10                    |     | 10   | μА    |

| I <sub>IN</sub> | Digital Input Current<br>SCK                 | $0V \le V_{IN} \le V_{CC}$ (Note 8)         | • | -10                    |     | 10   | μА    |

| C <sub>IN</sub> | Digital Input Capacitance CS, F <sub>0</sub> |                                             |   |                        | 10  |      | pF    |

| C <sub>IN</sub> | Digital Input Capacitance<br>SCK             | (Note 8)                                    |   |                        | 10  |      | pF    |

| V <sub>OH</sub> | High Level Output Voltage<br>SDO, BUSY       | $I_0 = -800 \mu A$                          | • | V <sub>CC</sub> - 0.5V |     |      | V     |

| V <sub>OL</sub> | Low Level Output Voltage<br>SDO, BUSY        | I <sub>0</sub> = 1.6mA                      | • |                        |     | 0.4V | V     |

| V <sub>OH</sub> | High Level Output Voltage<br>SCK             | I <sub>0</sub> = -800μA (Note 9)            | • | V <sub>CC</sub> - 0.5V |     |      | V     |

| V <sub>OL</sub> | Low Level Output Voltage<br>SCK              | I <sub>0</sub> = 1.6mA (Note 9)             | • |                        |     | 0.4V | V     |

| I <sub>OZ</sub> | Hi-Z Output Leakage<br>SDO                   |                                             | • | -10                    |     | 10   | μА    |

|                 | ·                                            | <u> </u>                                    |   |                        |     |      | 2440i |

# **POWER REQUIREMENTS** The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. (Note 3)

| SYMBOL          | PARAMETER       | CONDITIONS                            |   | MIN | TYP | MAX | UNITS |

|-----------------|-----------------|---------------------------------------|---|-----|-----|-----|-------|

| $V_{CC}$        | Supply Voltage  |                                       | • | 4.5 |     | 5.5 | V     |

| I <sub>CC</sub> | Supply Current  |                                       |   |     |     |     |       |

|                 | Conversion Mode | $\overline{CS} = 0V \text{ (Note 7)}$ | • |     | 8   | 11  | mA    |

|                 | Sleep Mode      | $\overline{CS} = V_{CC}$ (Note 7)     | • |     | 8   | 30  | μA    |

# TIMING CHARACTERISTICS The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. (Note 3)

| SYMBOL                 | PARAMETER                                           | CONDITIONS                                                             |   | MIN         | TYP                           | MAX         | UNITS     |

|------------------------|-----------------------------------------------------|------------------------------------------------------------------------|---|-------------|-------------------------------|-------------|-----------|

| f <sub>EOSC</sub>      | External Oscillator Frequency Range                 |                                                                        | • | 0.1         |                               | 20          | MHz       |

| t <sub>HEO</sub>       | External Oscillator High Period                     |                                                                        | • | 25          |                               | 10000       | ns        |

| t <sub>LEO</sub>       | External Oscillator Low Period                      |                                                                        | • | 25          |                               | 10000       | ns        |

| t <sub>CONV</sub>      | Conversion Time                                     | OSR = 256 (SDI = 0)<br>OSR = 32768 (SDI = 1)                           | • | 0.99<br>126 | 1.13<br>145                   | 1.33<br>170 | ms<br>ms  |

|                        |                                                     | External Oscillator (Note 10)                                          | • |             | 40000 • OSR<br>feosc          |             | ms        |

| f <sub>ISCK</sub>      | Internal SCK Frequency                              | Internal Oscillator (Note 9)<br>External Oscillator (Notes 9, 10)      | • | 0.8         | 0.9<br>f <sub>EOSC</sub> /10  | 1           | MHz<br>Hz |

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle                             | (Note 9)                                                               | • | 45          |                               | 55          | %         |

| f <sub>ESCK</sub>      | External SCK Frequency Range                        | (Note 8)                                                               | • |             |                               | 20          | MHz       |

| t <sub>LESCK</sub>     | External SCK Low Period                             | (Note 8)                                                               | • | 25          |                               |             | ns        |

| t <sub>HESCK</sub>     | External SCK High Period                            | (Note 8)                                                               | • | 25          |                               |             | ns        |

| t <sub>DOUT_ISCK</sub> | Internal SCK 32-Bit Data Output Time                | Internal Oscillator (Notes 9, 11)<br>External Oscillator (Notes 9, 10) | • | 41.6        | 35.3<br>320/f <sub>EOSC</sub> | 30.9        | μs<br>s   |

| t <sub>DOUT_ESCK</sub> | External SCK 32-Bit Data Output Time                | (Note 8)                                                               | • |             | 32/f <sub>ESCK</sub>          |             | S         |

| t <sub>1</sub>         | CS ↓ to SDO Low Z                                   |                                                                        | • | 0           |                               | 200         | ns        |

| t <sub>2</sub>         | CS ↑ to SDO High Z                                  |                                                                        | • | 0           |                               | 200         | ns        |

| t <sub>3</sub>         | $\overline{CS} \downarrow to \; SCK \downarrow$     | (Note 9)                                                               |   |             | 5                             |             | μS        |

| $\overline{t_4}$       | CS ↓ to SCK ↑                                       | (Note 8)                                                               |   |             | 5                             |             | μS        |

| t <sub>KQMAX</sub>     | SCK ↓ to SDO Valid                                  |                                                                        | • |             |                               | 200         | ns        |

| t <sub>KQMIN</sub>     | SDO Hold After SCK ↓                                | (Note 5)                                                               | • | 15          |                               |             | ns        |

| t <sub>5</sub>         | SCK Set-Up Before $\overline{\text{CS}} \downarrow$ |                                                                        | • | 50          |                               |             | ns        |

| t <sub>6</sub>         | SCK Hold After $\overline{\text{CS}}$ ↓             |                                                                        | • |             |                               | 50          | ns        |

| t <sub>7</sub>         | SDI Setup Before SCK ↑                              |                                                                        | • | 10          | Note 5                        |             | ns        |

| t <sub>8</sub>         | SDI Hold After SCK ↑                                |                                                                        | • | 10          | Note 5                        | <u> </u>    | ns        |

Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

Note 2: All voltage values are with respect to GND.

**Note 3:**  $V_{CC} = 4.5$  to 5.5V unless otherwise specified.

$V_{REF} = REF^+ - REF^-, V_{REFCM} = (REF^+ + REF^-)/2;$   $V_{IN} = IN^+ - IN^-, V_{INCM} = (IN^+ + IN^-)/2.$

Note 4: F<sub>0</sub> pin tied to GND or to external conversion clock source with f<sub>EOSC</sub> = 10MHz unless otherwise specified.

Note 5: Guaranteed by design, not subject to test.

Note 6: Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

Note 7: The converter uses the internal oscillator.

**Note 8:** The converter is in external SCK mode of operation such that the SCK pin is used as a digital input. The frequency of the clock signal driving SCK during the data output is  $f_{\mbox{\footnotesize ESCK}}$  and is expressed in Hz.

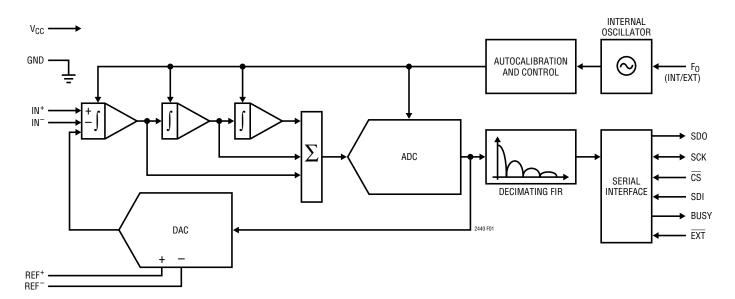

Note 9: The converter is in internal SCK mode of operation such that the SCK pin is used as a digital output. In this mode of operation, the SCK pin has a total equivalent load capacitance of  $C_{LOAD} = 20pF$ .

Note 10: The external oscillator is connected to the  $F_0$  pin. The external oscillator frequency, f<sub>EOSC</sub>, is expressed in Hz.

**Note 11:** The converter uses the internal oscillator.  $F_0 = 0V$ .

Note 12: Guaranteed by design and test correlation.

# TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

2440i

### TYPICAL PERFORMANCE CHARACTERISTICS

#### 20 $V_{CC} = 4.5V$ $V_{CC} = 5.5V, 5V$ V<sub>REF</sub> = 4.5V V<sub>REF</sub><sup>+</sup> = 4.5V $V_{REF} = 5V$ $V_{REF}^+ = 5V$ 15 FULL-SCALE ERROR (ppm OF V<sub>REF</sub>) $V_{REF}^{-} = GND$ $V_{REF}^- = GND$ 10 $V_{INCM} = 2.25V$ $V_{INCM} = 2.5V$ 4 5V OSR = 32768OSR = 32768 5 $F_0 = GND$ $F_0 = GND$ 0 -5 5V -10 -20

-Full-Scale Error vs Temperature

35

TEMPERATURE (°C)

65

95

125

-55

-25

5

**RMS Noise vs Temperature**

#### Offset Error vs Temperature

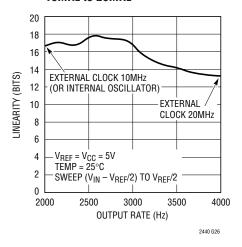

INL vs Output Rate (OSR = 128) External Clock Sweep 10MHz to 20MHz

RMS Noise vs Output Rate (OSR = 128) External Clock Sweep 10MHz to 20MHz

#### PIN FUNCTIONS

**GND** (Pins 1, 8, 9, 16): Ground. Multiple ground pins internally connected for optimum ground current flow and  $V_{CC}$  decoupling. Connect each one of these pins to a ground plane through a low impedance connection. All four pins must be connected to ground for proper operation.

$V_{CC}$  (Pin 2): Positive Supply Voltage. Bypass to GND (Pin 1) with a  $10\mu F$  tantalum capacitor in parallel with  $0.1\mu F$  ceramic capacitor as close to the part as possible.

**REF**<sup>+</sup> (**Pin 3**), **REF**<sup>-</sup> (**Pin 4**): Differential Reference Input. The voltage on these pins can have any value between GND and  $V_{CC}$  as long as the reference positive input, REF<sup>+</sup>, is maintained more positive than the reference negative input, REF<sup>-</sup>, by at least 0.1V.

IN+ (Pin 5), IN- (Pin 6): Differential Analog Input. The voltage on these pins can have any value between GND – 0.3V and  $V_{CC}$  + 0.3V. Within these limits the converter bipolar input range ( $V_{IN} = IN^+ - IN^-$ ) extends from –0.5 • ( $V_{REF}$ ) to 0.5 • ( $V_{REF}$ ). Outside this input range the converter produces unique overrange and underrange output codes.

**SDI (Pin 7):** Serial Data Input. This pin is used to select the speed/resolution of the converter. If SDI is grounded (pin compatible with LTC2410) the device outputs data at 880Hz with 21 bits effective resolution. By tying SDI HIGH, the converter enters the ultralow noise mode (200nV<sub>RMS</sub>) with simultaneous 50/60Hz rejection at 6.9Hz output rate. SDI may be driven logic HIGH or LOW anytime during the conversion or sleep state in order to change the speed/resolution. The conversion immediately following the data output cycle will be valid and performed at the newly selected output rate/resolution. SDI may also be programmed by a serial input data stream under control of SCK during the data output cycle. One of ten speed/resolution ranges (from 6.9Hz/200nV<sub>RMS</sub>) to 3.5kHz/21µV<sub>RMS</sub>) may be selected. The first conversion following a new selection is valid and performed at the newly selected speed/resolution.

**EXT** (**Pin 10**): Internal/External SCK Selection Pin. This pin is used to select internal or external SCK for outputting data. If EXT is tied low (pin compatible with the LTC2410), the device is in the external SCK mode and data is shifted out the device under the control of a user applied serial clock. If EXT is tied high, the internal serial clock mode is

selected. The device generates its own SCK signal and outputs this on the SCK pin. A framing signal BUSY (Pin 15) goes low indicating data is being output.

CS (Pin 11): Active LOW Digital Input. A LOW on this pin enables the SDO digital output and wakes up the ADC. Following each conversion the ADC automatically enters the Sleep mode and remains in this low power state as long as CS is HIGH. A LOW-to-HIGH transition on CS during the Data Output transfer aborts the data transfer and starts a new conversion.

**SDO** (Pin 12): Three-State Digital Output. During the Data Output period, this pin is used as serial data output. When the chip select  $\overline{CS}$  is HIGH ( $\overline{CS} = V_{CC}$ ) the SDO pin is in a high impedance state. During the Conversion and Sleep periods, this pin is used as the conversion status output. The conversion status can be observed by pulling  $\overline{CS}$  LOW.

**SCK (Pin 13):** Bidirectional Digital Clock Pin. In Internal Serial Clock Operation mode, SCK is used as digital output for the internal serial interface clock during the Data Output period. In External Serial Clock Operation mode, SCK is used as digital input for the external serial interface clock during the Data Output period. The Serial Clock Operation mode is determined by the logic level applied to the EXT pin.

**F<sub>0</sub> (Pin 14):** Frequency Control Pin. Digital input that controls the internal conversion clock. When F<sub>0</sub> is connected to V<sub>CC</sub> or GND, the converter uses its internal oscillator running at 9MHz. The conversion rate is determined by the selected OSR such that  $t_{CONV} = 0.04 \cdot OSR/9000$  ( $t_{CONV} = 1.137$ ms at OSR = 256,  $t_{CONV} = 146$ ms at OSR = 32768). The first null is located at 8/ $t_{CONV}$ , 7kHz at OSR = 256 and 55Hz (Simultaneous 50/60Hz) at OSR = 32768.

When  $F_0$  is driven by an oscillator with frequency  $f_{EOSC}$ , the conversion time becomes  $t_{CONV} = 40000 \cdot OSR/f_{EOSC}$  (in ms) and the first null remains  $8/t_{CONV}$ .

**BUSY (Pin 15):** Conversion in Progress Indicator. For compatibility with the LTC2410, this pin should not be tied to ground. This pin is HIGH while the conversion is in progress and goes LOW indicating the conversion is complete and data is ready. It remains low during the sleep and data output states. At the conclusion of the data output state, it goes HIGH indicating a new conversion has begun.

2440i

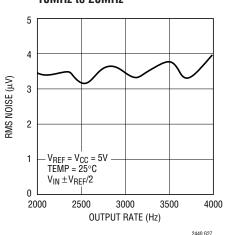

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

#### **TEST CIRCUITS**

# APPLICATIONS INFORMATION

#### **CONVERTER OPERATION**

#### **Converter Operation Cycle**

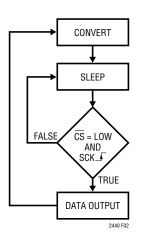

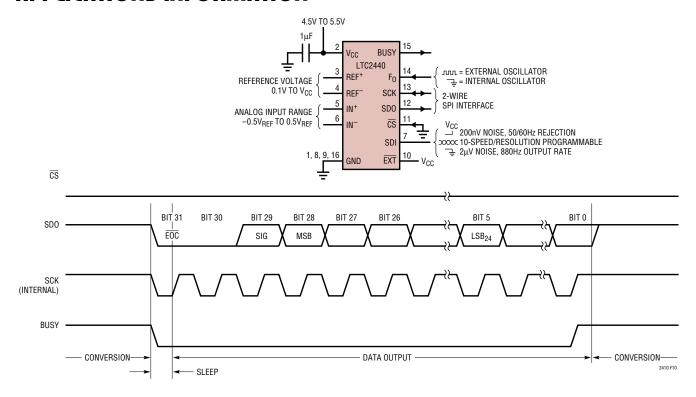

The LTC2440 is a high speed, delta-sigma analog-to-digital converter with an easy to use 3-wire serial interface (see Figure 1). Its operation is made up of three states. The converter operating cycle begins with the conversion, followed by the low power sleep state and ends with the data output (see Figure 2). The 3-wire interface consists of serial data output (SDO), serial clock (SCK) and chip select  $(\overline{CS})$ . The interface, timing, operation cycle and data out format is compatible with the LTC2410.

Figure 2. LTC2440 State Transition Diagram

2440

Initially, the LTC2440 performs a conversion. Once the conversion is complete, the device enters the sleep state. While in this sleep state, power consumption is reduced below  $10\mu A$ . The part remains in the sleep state as long as  $\overline{CS}$  is HIGH. The conversion result is held indefinitely in a static shift register while the converter is in the sleep state.

Once  $\overline{\text{CS}}$  is pulled LOW, the device begins outputting the conversion result. There is no latency in the conversion result. The data output corresponds to the conversion just performed. This result is shifted out on the serial data out pin (SDO) under the control of the serial clock (SCK). Data is updated on the falling edge of SCK allowing the user to reliably latch data on the rising edge of SCK (see Figure 3). The data output state is concluded once 32 bits are read out of the ADC or when  $\overline{\text{CS}}$  is brought HIGH. The device automatically initiates a new conversion and the cycle repeats.

Through timing control of the  $\overline{\text{CS}}$ , SCK and  $\overline{\text{EXT}}$  pins, the LTC2440 offers several flexible modes of operation (internal or external SCK). These various modes do not require programming configuration registers; moreover, they do not disturb the cyclic operation described above. These modes of operation are described in detail in the Serial Interface Timing Modes section.

#### Ease of Use

The LTC2440 data output has no latency, filter settling delay or redundant data associated with the conversion cycle. There is a one-to-one correspondence between the conversion and the output data. Therefore, multiplexing multiple analog voltages is easy. Speed/resolution adjustments may be made seamlessly between two conversions without settling errors.

The LTC2440 performs offset and full-scale calibrations every conversion cycle. This calibration is transparent to the user and has no effect on the cyclic operation described above. The advantage of continuous calibration is extreme stability of offset and full-scale readings with respect to time, supply voltage change and temperature drift.

#### **Power-Up Sequence**

The LTC2440 automatically enters an internal reset state when the power supply voltage  $V_{CC}$  drops below approximately 2.2V. This feature guarantees the integrity of the conversion result and of the serial interface mode selection.

When the  $V_{CC}$  voltage rises above this critical threshold, the converter creates an internal power-on-reset (POR) signal with a duration of approximately 0.5ms. The POR signal clears all internal registers. Following the POR signal, the LTC2440 starts a normal conversion cycle and follows the succession of states described above. The first conversion result following POR is accurate within the specifications of the device if the power supply voltage is restored within the operating range (4.5V to 5.5V) before the end of the POR time interval.

#### **Reference Voltage Range**

This converter accepts a truly differential external reference voltage. The absolute/common mode voltage specification for the REF<sup>+</sup> and REF<sup>-</sup> pins covers the entire range from GND to  $V_{CC}$ . For correct converter operation, the REF<sup>+</sup> pin must always be more positive than the REF<sup>-</sup> pin.

The LTC2440 can accept a differential reference voltage from 0.1V to  $V_{CC}$ . The converter output noise is determined by the thermal noise of the front-end circuits, and as such, its value in microvolts is nearly constant with reference voltage. A decrease in reference voltage will not significantly improve the converter's effective resolution. On the other hand, a reduced reference voltage will improve the converter's overall INL performance.

#### **Input Voltage Range**

The analog input is truly differential with an absolute/common mode range for the IN<sup>+</sup> and IN<sup>-</sup> input pins extending from GND - 0.3V to  $V_{CC}$  + 0.3V. Outside these limits, the ESD protection devices begin to turn on and the errors due to input leakage current increase rapidly. Within these limits, the LTC2440 converts the bipolar differential input signal,  $V_{IN}$  = IN<sup>+</sup> - IN<sup>-</sup>, from -FS = -0.5 •  $V_{REF}$  to +FS = 0.5 •  $V_{REF}$  where  $V_{REF}$  =

LINEAR

REF<sup>+</sup> – REF<sup>-</sup>. Outside this range, the converter indicates the overrange or the underrange condition using distinct output codes.

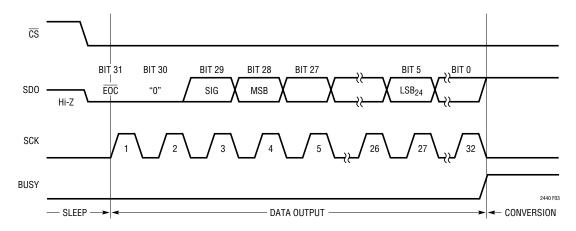

#### **Output Data Format**

The LTC2440 serial output data stream is 32 bits long. The first 3 bits represent status information indicating the sign and conversion state. The next 24 bits are the conversion result, MSB first. The remaining 5 bits are sub LSBs beyond the 24-bit level that may be included in averaging or discarded without loss of resolution. In the case of ultrahigh resolution modes, more than 24 effective bits of performance are possible (see Table 3). Under these conditions, sub LSBs are included in the conversion result and represent useful information beyond the 24-bit level. The third and fourth bit together are also used to indicate an underrange condition (the differential input voltage is below –FS) or an overrange condition (the differential input voltage is above +FS).

Bit 31 (first output bit) is the end of conversion (EOC) indicator. This bit is available at the SDO pin during the conversion and sleep states whenever the CS pin is LOW. This bit is HIGH during the conversion and goes LOW when the conversion is complete.

Bit 30 (second output bit) is a dummy bit (DMY) and is always LOW.

Bit 29 (third output bit) is the conversion result sign indicator (SIG). If  $V_{IN}$  is >0, this bit is HIGH. If  $V_{IN}$  is <0, this bit is LOW.

Bit 28 (fourth output bit) is the most significant bit (MSB) of the result. This bit in conjunction with Bit 29 also provides the underrange or overrange indication. If both Bit 29 and Bit 28 are HIGH, the differential input voltage is above +FS. If both Bit 29 and Bit 28 are LOW, the differential input voltage is below -FS.

The function of these bits is summarized in Table 1.

Table 1. LTC2440 Status Bits

| Input Range                            | Bit 31<br>EOC | Bit 30<br>DMY | Bit 29<br>SIG | Bit 28<br>MSB |

|----------------------------------------|---------------|---------------|---------------|---------------|

| $V_{IN} \ge 0.5 \bullet V_{REF}$       | 0             | 0             | 1             | 1             |

| $0V \le V_{IN} < 0.5 \bullet V_{REF}$  | 0             | 0             | 1             | 0             |

| $-0.5 \bullet V_{REF} \le V_{IN} < 0V$ | 0             | 0             | 0             | 1             |

| $V_{IN} < -0.5 \bullet V_{REF}$        | 0             | 0             | 0             | 0             |

Bits 28-5 are the 24-bit conversion result MSB first.

Bit 5 is the least significant bit (LSB).

Bits 4-0 are sub LSBs below the 24-bit level. Bits 4-0 may be included in averaging or discarded without loss of resolution.

Data is shifted out of the SDO pin under control of the serial clock (SCK), see Figure 3. Whenever  $\overline{\text{CS}}$  is HIGH, SDO remains high impedance.

In order to shift the conversion result out of the device, CS must first be driven LOW. EOC is seen at the SDO pin of the device once CS is pulled LOW. EOC changes real time from HIGH to LOW at the completion of a conversion. This signal may be used as an interrupt for an external

Figure 3. Output Data Timing

microcontroller. Bit 31 (EOC) can be captured on the first rising edge of SCK. Bit 30 is shifted out of the device on the first falling edge of SCK. The final data bit (Bit 0) is shifted out on the falling edge of the 31st SCK and may be latched on the rising edge of the 32nd SCK pulse. On the falling edge of the 32nd SCK pulse. On the falling edge of the 32nd SCK pulse, SDO goes HIGH indicating the initiation of a new conversion cycle. This bit serves as  $\overline{EOC}$  (Bit 31) for the next conversion cycle. Table 2 summarizes the output data format.

As long as the voltage on the IN+ and IN- pins is maintained within the -0.3V to  $(V_{CC}+0.3V)$  absolute maximum operating range, a conversion result is generated for any differential input voltage  $V_{IN}$  from  $-FS=-0.5 \bullet V_{REF}$  to +FS=0.5  $\bullet V_{REF}$ . For differential input voltages greater than +FS, the conversion result is clamped to the value corresponding to the +FS+1LSB. For differential input voltages below -FS, the conversion result is clamped to the value corresponding to -FS - 1LSB.

#### SERIAL INTERFACE PINS

The LTC2440 transmits the conversion results and receives the start of conversion command through a synchronous 2-, 3- or 4-wire interface. During the conversion and sleep states, this interface can be used to assess the converter status and during the data output state it is used to read the conversion result and program the speed/resolution.

#### Serial Clock Input/Output (SCK)

The serial clock signal present on SCK (Pin 13) is used to synchronize the data transfer. Each bit of data is shifted out the SDO pin on the falling edge of the serial clock.

In the Internal SCK mode of operation, the SCK pin is an output and the LTC2440 creates its own serial clock. In the External SCK mode of operation, the SCK pin is used as input. The internal or external SCK mode is selected by tying EXT (Pin 10) LOW for external SCK and HIGH for internal SCK.

#### Serial Data Output (SDO)

The serial data output pin, SDO (Pin 12), provides the result of the last conversion as a serial bit stream (MSB first) during the data output state. In addition, the SDO pin is used as an end of conversion indicator during the conversion and sleep states.

When  $\overline{\text{CS}}$  (Pin 11) is HIGH, the SDO driver is switched to a high impedance state. This allows sharing the serial interface with other devices. If  $\overline{\text{CS}}$  is  $\underline{\text{LOW}}$  during the convert or sleep state, SDO will output EOC. If  $\overline{\text{CS}}$  is LOW during the conversion phase, the  $\overline{\text{EOC}}$  bit appears  $\overline{\text{HIGH}}$  on the SDO pin. Once the conversion is complete,  $\overline{\text{EOC}}$  goes LOW. The device remains in the  $\underline{\text{sleep}}$  state until the first rising edge of SCK occurs while  $\overline{\text{CS}}$  = LOW.

Table 2. LTC2440 Output Data Format

| Differential Input Voltage<br>V <sub>IN</sub> * | Bit 31<br>EOC | Bit 30<br>DMY | Bit 29<br>SIG | Bit 28<br>MSB | Bit 27 | Bit 26 | Bit 25 | <br>Bit 0 |

|-------------------------------------------------|---------------|---------------|---------------|---------------|--------|--------|--------|-----------|

| $V_{IN}^* \ge 0.5 \bullet V_{REF}^{**}$         | 0             | 0             | 1             | 1             | 0      | 0      | 0      | <br>0     |

| 0.5 • V <sub>REF</sub> ** − 1LSB                | 0             | 0             | 1             | 0             | 1      | 1      | 1      | <br>1     |

| 0.25 • V <sub>REF</sub> **                      | 0             | 0             | 1             | 0             | 1      | 0      | 0      | <br>0     |

| 0.25 • V <sub>REF</sub> ** – 1LSB               | 0             | 0             | 1             | 0             | 0      | 1      | 1      | <br>1     |

| 0                                               | 0             | 0             | 1             | 0             | 0      | 0      | 0      | <br>0     |

| -1LSB                                           | 0             | 0             | 0             | 1             | 1      | 1      | 1      | <br>1     |

| -0.25 • V <sub>REF</sub> **                     | 0             | 0             | 0             | 1             | 1      | 0      | 0      | <br>0     |

| -0.25 • V <sub>REF</sub> ** − 1LSB              | 0             | 0             | 0             | 1             | 0      | 1      | 1      | <br>1     |

| -0.5 • V <sub>REF</sub> **                      | 0             | 0             | 0             | 1             | 0      | 0      | 0      | <br>0     |

| V <sub>IN</sub> * < −0.5 • V <sub>REF</sub> **  | 0             | 0             | 0             | 0             | 1      | 1      | 1      | <br>1     |

<sup>\*</sup>The differential input voltage  $V_{IN} = IN^+ - IN^-$ . \*\*The differential reference voltage  $V_{REF} = REF^+ - REF^-$ .

#### Chip Select Input (CS)

The active LOW chip select,  $\overline{CS}$  (Pin 11), is used to test the conversion status and to enable the data output transfer as described in the previous sections.

In addition, the  $\overline{\text{CS}}$  signal can be used to trigger a new conversion cycle before the entire serial data transfer has been completed. The LTC2440 will abort any serial data transfer in progress and start a new conversion cycle anytime a LOW-to-HIGH transition is detected at the  $\overline{\text{CS}}$  pin after the converter has entered the data output state (i.e., after the fifth falling edge of SCK occurs with  $\overline{\text{CS}}$  = LOW).

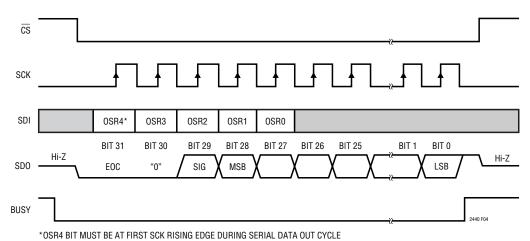

#### Serial Data Input (SDI)

The serial data input (SDI, Pin 7) is used to select the speed/resolution of the LTC2440. A simple 2-speed control is selectable by either driving SDI HIGH or LOW. If SDI is grounded (pin compatible with LTC2410) the device outputs data at 880Hz with 21 bits effective resolution. By tying SDI HIGH, the converter enters the ultralow noise mode (200nV $_{RMS}$ ) with simultaneous 50/60Hz rejection at 6.9Hz output rate. SDI may be driven logic HIGH or LOW anytime during the conversion or sleep state in order to change the speed/resolution. The conversion immediately following the data output cycle will be valid and performed at the newly selected output rate/resolution.

Changing SDI logic state during the data output cycle should be avoided as speed resolution other than 6.9Hz or 880Hz may be selected. For example, if SDI is changed from logic 0 to logic 1 after the second rising edge of SCK, the conversion rate will change from 880Hz to 55Hz (see Table 3: OSR4 = 0, OSR3 = 0, OSR2 = 1, OSR1 = 1 and OSR0 = 1). If SDI remains HIGH, the conversion rate will switch to the desired 6.9Hz speed immediately following the conversion at 55Hz. The 55Hz rate conversion cycle will be a valid result as well as the first 6.9Hz result. On the other hand, if SDI is changed to a 1 anytime before the first rising edge of SCK, the following conversion rate will become 6.9Hz. If SDI is changed to a 1 after the 5th rising edge of SCK, the next conversion will remain 880Hz while all subsequent conversions will be at 6.9Hz.

SDI may also be programmed by a serial input data stream under control of SCK during the data output cycle, see Figure 4. One of ten speed/resolution ranges (from 6.9Hz/  $200nV_{RMS}$  to  $3.5kHz/21\mu V_{RMS})$  may be selected, see Table 3. The conversion following a new selection is valid and performed at the newly selected speed/resolution.

#### **BUSY**

The BUSY output (Pin 15) is used to monitor the state of conversion, data output and sleep cycle. While the part is converting, the BUSY pin is HIGH. Once the conversion is complete, BUSY goes LOW indicating the conversion is complete and data out is ready. The part now enters the LOW power sleep state. BUSY remains LOW while data is shifted out of the device. It goes HIGH at the conclusion of the data output cycle indicating a new conversion has begun. This rising edge may be used to flag the completion of the data read cycle.

#### **SERIAL INTERFACE TIMING MODES**

The LTC2440's 2-, 3- or 4-wire interface is SPI and MICROWIRE compatible. This interface offers several flexible modes of operation. These include internal/external serial clock, 2- or 3-wire I/O, single cycle conversion and autostart. The following sections describe each of these serial interface timing modes in detail. In all these cases, the converter can use the internal oscillator ( $F_0 = LOW$ ) or an external oscillator connected to the  $F_0$  pin. Refer to Table 4 for a summary.

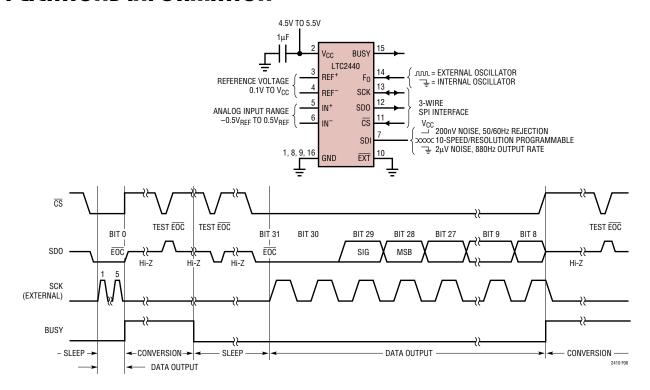

# External Serial Clock, Single Cycle Operation (SPI/MICROWIRE Compatible)

This timing mode uses an external serial clock to shift out the conversion result and a CS signal to monitor and control the state of the conversion cycle, see Figure 5.

The serial clock mode is selected by the EXT pin. To select the external serial clock mode,  $\overline{\text{EXT}}$  must be tied low.

The serial data output pin (SDO) is Hi-Z as long as CS is HIGH. At any time during the conversion cycle,  $\overline{\text{CS}}$  may be pulled  $\underline{\text{LOW}}$  in order to monitor the state of the converter. While  $\overline{\text{CS}}$  is pulled LOW,  $\overline{\text{EOC}}$  is output to the SDO pin.

Figure 4. SDI Speed/Resolution Programming

Table 3. SDI Speed/Resolution Programming

|      |      |      |      |      | CONVER                 | SION RATE                  |              |      |         |

|------|------|------|------|------|------------------------|----------------------------|--------------|------|---------|

| OSR4 | OSR3 | OSR2 | OSR1 | 0SR0 | INTERNAL<br>9MHz CLOCK | EXTERNAL<br>10.24MHz CLOCK | RMS<br>Noise | ENOB | OSR     |

| Χ    | 0    | 0    | 0    | 1    | 3.52kHz                | 4kHz                       | 23μV         | 17   | 64      |

| Χ    | 0    | 0    | 1    | 0    | 1.76kHz                | 2kHz                       | 3.5µV        | 20   | 128     |

| 0    | 0    | 0    | 0    | 0    | 880Hz                  | 1kHz                       | 2μV          | 213  | 256*    |

| Χ    | 0    | 0    | 1    | 1    | 880Hz                  | 1kHz                       | 2μV          | 21.3 | 256     |

| Χ    | 0    | 1    | 0    | 0    | 440Hz                  | 500Hz                      | 1.4μV        | 21.8 | 512     |

| Χ    | 0    | 1    | 0    | 1    | 220Hz                  | 250Hz                      | 1μV          | 22.4 | 1024    |

| Χ    | 0    | 1    | 1    | 0    | 110Hz                  | 125Hz                      | 750nV        | 22.9 | 2048    |

| Χ    | 0    | 1    | 1    | 1    | 55Hz                   | 62.5Hz                     | 510nV        | 23.4 | 4096    |

| Χ    | 1    | 0    | 0    | 0    | 27.5Hz                 | 31.25Hz                    | 375nV        | 24   | 8192    |

| Χ    | 1    | 0    | 0    | 1    | 13.75Hz                | 15.625Hz                   | 250nV        | 24.4 | 16384   |

| Χ    | 1    | 1    | 1    | 1    | 6.875Hz                | 7.8125Hz                   | 200nV        | 24.6 | 32768** |

<sup>\*\*</sup>Address allows tying SDI HIGH \*Additional address to allow tying SDI LOW

Table 4. LTC2440 Interface Timing Modes

| Configuration                                   | SCK<br>Source | Conversion<br>Cycle<br>Control | Data<br>Output<br>Control | Connection<br>and<br>Waveforms |

|-------------------------------------------------|---------------|--------------------------------|---------------------------|--------------------------------|

| External SCK, Single Cycle Conversion           | External      | CS and SCK                     | CS and SCK                | Figures 5, 6                   |

| External SCK, 2-Wire I/O                        | External      | SCK                            | SCK                       | Figure 7                       |

| Internal SCK, Single Cycle Conversion           | Internal      | CS↓                            | CS↓                       | Figures 8, 9                   |

| Internal SCK, 2-Wire I/O, Continuous Conversion | Internal      | Continuous                     | Internal                  | Figure 10                      |

LINEAR TECHNOLOGY

Figure 5. External Serial Clock, Single Cycle Operation

$\underline{EOC}$  = 1 (BUSY = 1) while a conversion is in progress and  $\overline{EOC}$  = 0 (BUSY = 0) if the device is in the sleep state. Independent of  $\overline{CS}$ , the device automatically enters the low power sleep state once the conversion is complete.

When the device is in the sleep state (EOC = 0), its conversion result is held in an internal static shift register. The device remains in the sleep state until the first rising edge of SCK is seen. Data is shifted out the SDO pin on each falling edge of SCK. This enables external circuitry to latch the output on the rising edge of SCK.  $\overline{EOC}$  can be latched on the first rising edge of SCK and the last bit of the conversion result can be latched on the 32nd rising edge of SCK. On the 32nd falling edge of SCK, the device begins a new conversion. SDO goes HIGH ( $\overline{EOC}$  = 1) and BUSY goes HIGH indicating a conversion is in progress.

At the conclusion of the data cycle, CS may remain LOW and EOC monitored as an end-of-conversion interrupt. Alternatively, CS may be driven HIGH setting SDO to Hi-Z and BUSY monitored for the completion of a conversion. As described above, CS may be pulled LOW at any time in order to monitor the conversion status on the SDO pin.

Typically, CS remains LOW during the data output state. However, the data output state may be aborted by pulling CS HIGH anytime between the fifth falling edge (SDI must be properly loaded each cycle) and the 32nd falling edge of SCK, see Figure 6. On the rising edge of  $\overline{\text{CS}}$ , the device aborts the data output state and immediately initiates a new conversion. This is useful for systems not requiring all 32 bits of output data, aborting an invalid conversion cycle or synchronizing the start of a conversion.

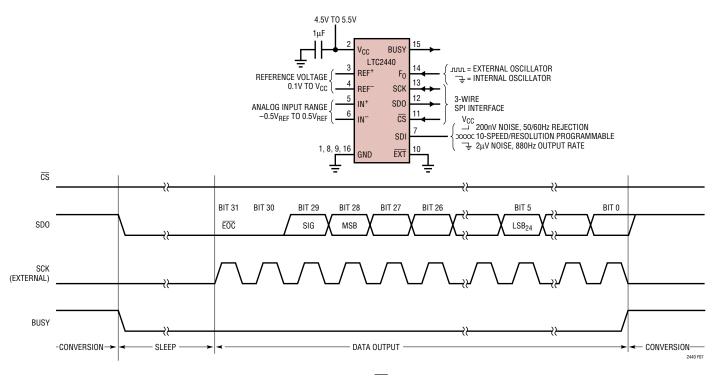

#### External Serial Clock, 2-Wire I/O

This timing mode utilizes a 2-wire serial I/O interface. The conversion result is shifted out of the device by an externally generated serial clock (SCK) signal, see Figure 7. CS may be permanently tied to ground, simplifying the user interface or isolation barrier. The external serial clock mode is selected by tying EXT LOW.

Since CS is tied LOW, the end-of-conversion (EOC) can be continuously monitored at the SDO pin during the convert and sleep states. Conversely, BUSY (Pin 15) may be used to monitor the status of the conversion cycle. EOC or BUSY may be used as an interrupt to an external controller

2440i

Figure 6. External Serial Clock, Reduced Data Output Length

Figure 7. External Serial Clock,  $\overline{CS} = 0$  Operation (2-Wire)

/ LINEAR

indicating the conversion result is ready. EOC = 1 (BUSY = 1) while the conversion is in progress and EOC = 0 (BUSY = 0) once the conversion enters the low power sleep state. On the falling edge of EOC/BUSY, the conversion result is loaded into an internal static shift register. The device remains in the sleep state until the first rising edge of SCK. Data is shifted out the SDO pin on each falling edge of SCK enabling external circuitry to latch data on the rising edge of SCK. EOC can be latched on the first rising edge of SCK. On the 32nd falling edge of SCK, SDO and BUSY go HIGH (EOC = 1) indicating a new conversion has begun.

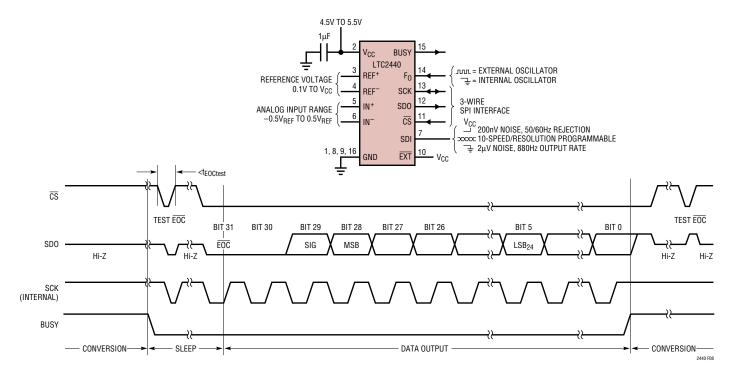

#### Internal Serial Clock, Single Cycle Operation

This timing mode uses an internal serial clock to shift out the conversion result and a  $\overline{CS}$  signal to monitor and control the state of the conversion cycle, see Figure 8.

<u>In order</u> to select the internal serial clock timing mode, the EXT pin must be tied HIGH.

The serial data output pin (SDO) is Hi-Z as long as  $\overline{CS}$  is HIGH. At any time during the conversion cycle,  $\overline{CS}$  may be pulled LOW in order to monitor the state of the converter.

Once  $\overline{CS}$  is pulled LOW, SCK goes LOW and  $\overline{EOC}$  is output to the SDO pin.  $\overline{EOC}$  = 1 while a conversion is in progress and  $\overline{EOC}$  = 0 if the device is in the sleep state. Alternatively, BUSY (Pin 15) may be used to monitor the status of the conversion in progress. BUSY is HIGH during the conversion and goes LOW at the conclusion. It remains LOW until the result is read from the device.

When testing EOC, if the conversion is complete (EOC = 0), the device will exit the sleep state and enter the data output state if  $\overline{CS}$  remains LOW. In order to prevent the device from exiting the low power sleep state,  $\overline{CS}$  must be pulled HIGH before the first rising edge of SCK. In the internal SCK timing mode, SCK goes HIGH and the device begins outputting data at time  $t_{EOCtest}$  after the falling edge of  $\overline{CS}$  (if  $\overline{EOC}$  = 0) or  $t_{EOCtest}$  after  $\overline{EOC}$  goes LOW (if  $\overline{CS}$  is LOW during the falling edge of  $\overline{EOC}$ ). The value of  $t_{EOCtest}$  is 500ns. If  $\overline{CS}$  is pulled HIGH before time  $t_{EOCtest}$ , the device remains in the sleep state. The conversion result is held in the internal static shift register.

If  $\overline{\text{CS}}$  remains LOW longer than  $t_{\text{EOCtest}}$ , the first rising edge of SCK will occur and the conversion result is serially shifted out of the SDO pin. The data output cycle begins on

Figure 8. Internal Serial Clock, Single Cycle Operation

this first rising edge of SCK and concludes after the 32nd rising edge. Data is shifted out the SDO pin on each falling edge of SCK. The internally generated serial clock is output to the SCK pin. This signal may be used to shift the conversion result into external circuitry.  $\overline{EOC}$  can be latched on the first rising edge of SCK and the last bit of the conversion result on the 32nd rising edge of SCK. After the 32nd rising edge, SDO goes HIGH ( $\overline{EOC}$  = 1), SCK stays HIGH and a new conversion starts.

Typically,  $\overline{CS}$  remains LOW during the data output state. However, the data output state may be aborted by pulling  $\overline{CS}$  HIGH anytime between the first and 32nd rising edge of SCK, see Figure 9. In order to properly select the OSR for the conversion following a data abort, five SCK rising edges must be seen prior to performing a data out abort (pulling  $\overline{CS}$  HIGH). If  $\overline{CS}$  is pulled high prior to the fifth SCK falling edge, the OSR selected depends on the number of SCK signals seen prior to data abort, where subsequent nonaborted conversion cycles return to the programmed OSR. On the rising edge of  $\overline{CS}$ , the device aborts the data output state and immediately initiates a new conversion.

This is useful for systems not requiring all 32 bits of output data, aborting an invalid conversion cycle, or synchronizing the start of a conversion.

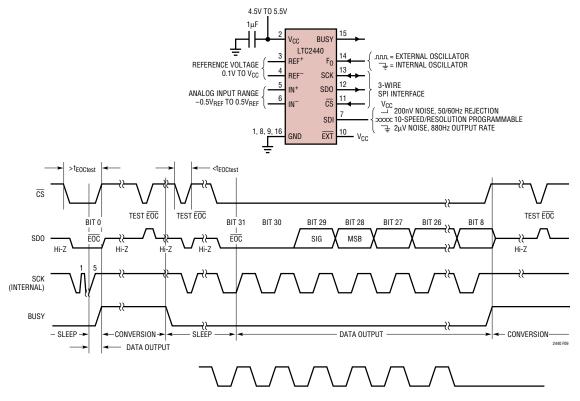

# Internal Serial Clock, 2-Wire I/O, Continuous Conversion

This timing mode uses a 2-wire, all output (SCK and SDO) interface. The conversion result is shifted out of the device by an internally generated serial clock (SCK) signal, see Figure 10.  $\overline{\text{CS}}$  may be permanently tied to ground, simplifying the user interface or isolation barrier. The internal serial clock mode is selected by tying  $\overline{\text{EXT}}$  HIGH.

During the conversion, the SCK and the serial data output pin (SDO) are HIGH ( $\overline{EOC}$  = 1) and BUSY = 1. Once the conversion is complete, SCK, BUSY and SDO go LOW ( $\overline{EOC}$  = 0) indicating the conversion has finished and the device has entered the low power sleep state. The part remains in the sleep state a minimum amount of time ( $\approx 500$ ns) then immediately begins outputting data. The data output cycle begins on the first rising edge of SCK and

Figure 9. Internal Serial Clock, Reduced Data Output Length

LINEAR TECHNOLOGY

Figure 10. Internal Serial Clock, Continuous Operation

ends after the 32nd rising edge. Data is shifted out the SDO pin on each falling edge of SCK. The internally generated serial clock is output to the SCK pin. This signal may be used to shift the conversion result into external circuitry.  $\overline{EOC}$  can be latched on the first rising edge of SCK and the last bit of the conversion result can be latched on the 32nd rising edge of SCK. After the 32nd rising edge, SDO goes HIGH ( $\overline{EOC}$  = 1) indicating a new conversion is in progress. SCK remains HIGH during the conversion.

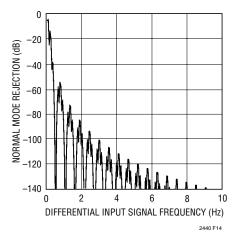

#### **Normal Mode Rejection and Antialiasing**

One of the advantages delta-sigma ADCs offer over conventional ADCs is on-chip digital filtering. Combined with a large oversampling ratio, the LTC2440 significantly simplifies antialiasing filter requirements.

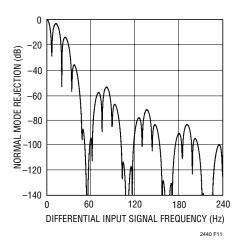

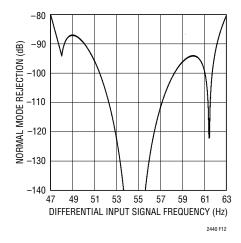

The LTC2440's speed/resolution is determined by the over sample ratio (OSR) of the on-chip digital filter. The OSR ranges from 64 for 3.5kHz output rate to 32,768 for 6.9Hz output rate. The value of OSR and the sample rate  $f_{S}$  determine the filter characteristics of the device. The first NULL of the digital filter is at  $f_{N}$  and multiples of  $f_{N}$  where

$f_N = f_S/OSR$ , see Figure 11 and Table 5. The rejection at the frequency  $f_N \pm 14\%$  is better than 80dB, see Figure 12.

If  $F_0$  is grounded,  $f_S$  is set by the on-chip oscillator at 1.8MHz±5% (over supply and temperature variations). At an OSR of 32,768, the first NULL is at  $f_N$  = 55Hz and the no latency output rate is  $f_N/8$  = 6.9Hz. At the maximum OSR,

Figure 11. LTC2440 Normal Mode Rejection (Internal Oscillator)

2440

Table 5. OSR vs Notch Frequency ( $f_N$ ) (with Internal Oscillator Running at 9MHz)

| OSR    | NOTCH (f <sub>N</sub> ) |

|--------|-------------------------|

| 64     | 28.16kHz                |

| 128    | 14.08kHz                |

| 256    | 7.04kHz                 |

| 512    | 3.52kHz                 |

| 1024   | 1.76kHz                 |

| 2048   | 880Hz                   |

| 4096   | 440Hz                   |

| 8192   | 220Hz                   |

| 16384  | 110Hz                   |

| 32768* | 55Hz                    |

<sup>\*</sup>Simultaneous 50/60 rejection

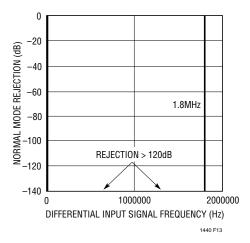

the noise performance of the device is  $200nV_{RMS}$  with better than 80dB rejection of  $50Hz \pm 2\%$  and  $60Hz \pm 2\%$ . Since the OSR is large (32,768) the wide band rejection is extremely large and the antialiasing requirements are simple. The first multiple of  $f_S$  occurs at  $55Hz \cdot 32,768 = 1.8MHz$ , see Figure 13.

The first NULL becomes  $f_N = 7.04 kHz$  with an OSR of 256 (an output rate of 880Hz) and  $F_0$  grounded. While the NULL has shifted, the sample rate remains constant. As a result of constant modulator sampling rate, the linearity, offset and full-scale performance remains unchanged as does the first multiple of  $f_S$ .

Figure 12. LTC2440 Normal Mode Rejection (Internal Oscillator)

Figure 13. LTC2440 Normal Mode Rejection (Internal Oscillator)

The sample rate  $f_S$  and NULL  $f_N$ , my also be adjusted by driving the  $F_O$  pin with an external oscillator. The sample rate is  $f_S = f_{EOSC}/5$ , where  $f_{EOSC}$  is the frequency of the clock applied to  $F_O$ . Combining a large OSR with a reduced sample rate leads to notch frequencies  $f_N$  near DC while maintaining simple antialiasing requirements. A 100kHz clock applied to  $F_O$  results in a NULL at 0.6Hz plus all harmonics up to 20kHz, see Figure 14. This is useful in applications requiring digitalization of the DC component of a noisy input signal and eliminates the need of placing a 0.6Hz filter in front of the ADC.

An external oscillator operating from 100kHz to 20MHz can be implemented using the LTC1799 (resistor set SOT-23 oscillator), see Figure 15. By floating pin 4 (DIV) of the LTC1799, the output oscillator frequency is:

$$f_{OSC} = 10MHz \cdot \left(\frac{10k}{10 \cdot R_{SET}}\right)$$

The normal mode rejection characteristic shown in Figure 14 is achieved by applying the output of the LTC1799 (with  $R_{SET}$  = 100k) to the  $F_0$  pin on the LTC2440 with SDI tied HIGH (OSR = 32768).

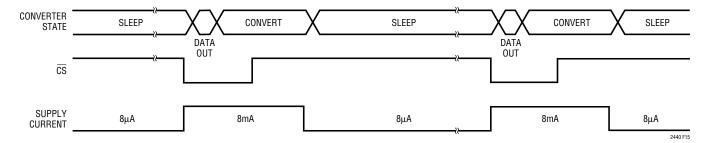

#### **Reduced Power Operation**

In addition to adjusting the speed/resolution of the LTC2440, the speed/resolution/power dissipation may also be adjusted using the automatic sleep mode. During the conversion cycle, the LTC2440 draws 8mA supply current independent of the programmed speed. Once the conversion cycle is completed, the device automatically enters a low power sleep state drawing 8µA. The device remains in this state as long as  $\overline{CS}$  is HIGH and data is not shifted out. By adjusting the duration of the sleep state (hold  $\overline{CS}$  HIGH longer) and the duration of the conversion cycle (programming OSR) the DC power dissipation can be reduced, see Figure 16.

For example, if the OSR is programmed at the fastest rate (OSR = 64,  $t_{CONV}$  = 0.285ms) and the sleep state is 10ms, the effective output rate is approximately 100Hz while the average supply current is reduced to 240 $\mu$ A. By further extending the sleep state to 100ms, the effective output rate of 10Hz draws on average 30 $\mu$ A. Noise, power, and speed can be optimized by adjusting the OSR (Noise/Speed) and sleep mode duration (Power).

Figure 14. LTC2440 Normal Mode Rejection (External Oscillator at 90kHz)

# TYPICAL APPLICATION

Figure 15. Reduced Power Timing Mode

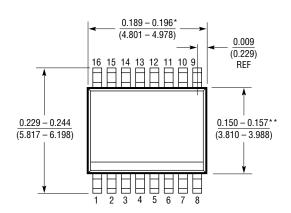

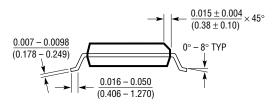

# PACKAGE DESCRIPTION

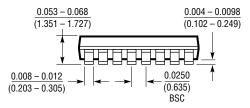

# **GN Package 16-Lead Plastic SSOP (Narrow .150 Inch)** (Reference LTC DWG # 05-08-1641)

- \* DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\* DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

GN16 (SSOP) 1098

# TYPICAL APPLICATION

Figure 16. Simple External Clock Source

# **RELATED PARTS**

| PART NUMBER                | DESCRIPTION                                                         | COMMENTS                                                                  |

|----------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------|

| LT1025                     | Micropower Thermocouple Cold Junction Compensator                   | 80μA Supply Current, 0.5°C Initial Accuracy                               |

| LTC1043                    | Dual Precision Instrumentation Switched Capacitor<br>Building Block | Precise Charge, Balanced Switching, Low Power                             |

| LTC1050                    | Precision Chopper Stabilized Op Amp                                 | No External Components 5μV Offset, 1.6μV <sub>P-P</sub> Noise             |

| LT1236A-5                  | Precision Bandgap Reference, 5V                                     | 0.05% Max, 5ppm/°C Drift                                                  |

| LT1461                     | Micropower Series Reference, 2.5V                                   | 0.04% Max, 3ppm/°C Max Drift                                              |

| LTC1592                    | Ultraprecise 16-Bit SoftSpan™ DAC                                   | Six Programmable Output Ranges                                            |

| LTC1655                    | 16-Bit Rail-to-Rail Micropower DAC                                  | ±1LSB DNL, 600μA, Internal Reference, SO-8                                |

| LTC1799                    | Resistor Set SOT-23 Oscillator                                      | Single Resistor Frequency Set                                             |

| LTC2053                    | Rail-to-Rail Instrumentation Amplifier                              | 10μV Offset with 50nV/°C Drift, 2.5μV <sub>P-P</sub> Noise 0.01Hz to 10Hz |

| LTC2400                    | 24-Bit, No Latency $\Delta\Sigma$ ADC in SO-8                       | 0.3ppm Noise, 4ppm INL, 10ppm Total Unadjusted Error, 200μA               |

| LTC2401/LTC2402            | 1-/2-Channel, 24-Bit, No Latency $\Delta\Sigma$ ADC in MSOP         | 0.6ppm Noise, 4ppm INL, 10ppm Total Unadjusted Error, 200μA               |

| LTC2404/LTC2408            | 4-/8-Channel, 24-Bit, No Latency $\Delta\Sigma$ ADC                 | 0.3ppm Noise, 4ppm INL, 10ppm Total Unadjusted Error, 200μA               |

| LTC2410/LTC2413            | 24-Bit, No Latency $\Delta\Sigma$ ADC                               | 800nV <sub>RMS</sub> Noise, 5ppm INL/Simultaneous 50Hz/60Hz Rejection     |

| LTC2411                    | 24-Bit, No Latency $\Delta\Sigma$ ADC in MSOP                       | 1.45µV <sub>RMS</sub> Noise, 6ppm INL                                     |

| LTC2413                    | 24-Bit, No Latency $\Delta\Sigma$ ADC                               | Simultaneous 50Hz/60Hz Rejection, 800nV <sub>RMS</sub> Noise              |

| LTC2420LTC2424/<br>LTC2428 | 1-/4-/8-Channel, 20-Bit, No Latency $\Delta\Sigma$ ADCs             | 1.2ppm Noise, 8ppm INL, Pin Compatible with LTC2400/<br>LTC2404/LTC2408   |

SoftSpan is a trademark of Linear Technology Corporation.